# 多层介质中通孔结构准静态电容参数的提取 1

#### 宋 犇 洪 伟

(东南大学毫米波国家重点实验室 南京 210096)

搞 要 本文采用维数缩减技术 (DRT) 提取了多层介质中通孔结构的准静态电容参数。由于该方法充分利用了集成电路结构分层性的特点,从而可以很方便地处理任意的介质层数和结构参数,而仅需很少的计算时间和内存。文中的计算结果与 Ansoft 软件结果符合较好。

关键词 参数提取,准静态电容,三维互连,通孔结构,维数缩减技术

中图号 TN431.2

#### 1 引 言

近几年来,高速数字集成电路在电路的密度和时钟频率两个方面有了很大的发展。高密度和高时钟频率使得各种复杂的互连对电路的电性能有了很大的影响,因此如何快速准确地提取多层介质中多导体互连结构的电参数成为当前研究的新热点。多层介质中的通孔结构是高速数字集成电路和多芯片组件 (MCM) 中常见的一种三维互连结构,自 1988 年以来已有多篇文献对其准静态电容进行了分析 [1-5],其中文献 [1-4]用的是积分方程类方法,介质只有两层,且不考虑导体厚度,文献 [5]为能利用圆柱对称性达到减化计算的目的,而将上下两导带完全丢弃,由此可见上述文献所用方法都有模型简化过多的不足之处,并不能很好地满足工程应用的需要。

为了就更精确的模型,更为任意的介质层数,做出更为准确快捷的分析,本文决定采用新近提出的一种方法——维数缩减技术。这种方法充分利用了集成电路互连结构的分层性特点来发展快速算法,它将复杂的三维结构切割成许多个沿垂直于介质交界面方向均匀的波导,每个波导中的场用模式函数展开,然后用模式匹配法求解。通过这种方法,原来复杂的三维结构被分解为二维结构,而其中许多二维结构的模式函数可解析地写出(如纯介质层),因此能大大减少计算所需的时间和内存。此外,对不能解析写出模式函数的二维结构,则可用数值办法获得数值模式函数,因此该方法又可以处理不同形状的二维结构,具有充分的灵活性。

## 2 维数缩减技术的原理

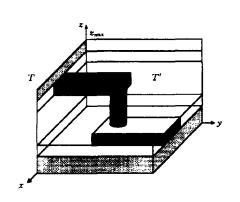

由于目前集成电路的时钟频率仍然低于 500MHz, 因此有效信号的频率低于 10GHz, 进行准静态分析已经足够精确。 VLSI 中典型的通孔互连结构如图 1 所示, 埋于多层介质中走向相同但位于不同层中的上下两信号线通过一金属柱垂直相连。由于整个结构关于面 T-T' 对称,故可将面 T-T' 当作磁壁 (M.W),只分析一半结构的电容,结果乘以 2 即得总电容。又由准静态的定义,距离不连续性足够远且垂直于信号线的两个面以及平行于信号线的一个面也可视为磁壁,这样四个磁壁就将三维不连续区域割裂出来,可以单独进行分析,而磁壁以外的部分已

<sup>1 1996-04-24</sup> 收到, 1997-02-04 定稿

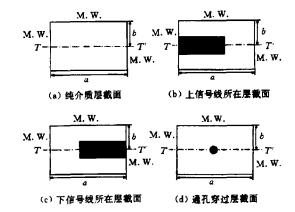

退化为二维结构,可以方便地计算其电容矩阵 [6-8].现在,问题的焦点集中于为磁壁所包围的三维结构上。这个结构可看作沿垂直于介质交界面方向的多个二维结构的级联,这些结构的四壁均为磁壁,图 1 中四种典型层的截面如图 2 所示。

图 1 埋于多层介质中的通孔结构

图 2 多层介质中通孔结构的四个典型层的截面

对于准静态 TEM 模分析, 电位函数满足拉普拉斯方程:

$$\Delta \phi = 0. \tag{1}$$

在各层介质交界面上的边界条件为

$$\phi_i = \phi_{i+1}, \qquad \varepsilon_i \partial \phi_i / \partial z = \varepsilon_{i+1} \partial \phi_{i+1} / \partial z;$$

(2)

而沿各层横向, 其边界条件则需要分层给出。在介质层中(如图 2(a) 所示), 边界条件为

$$\partial \phi / \partial x = 0, \quad x = 0, a; \quad \partial \phi / \partial y = 0, \quad y = 0, b;$$

(3)

而在含有导体的各层 (如图 2(b), 2(c), 2(d) 所示), 边界条件为

$$\phi = V$$

, 导体边界上;  $\partial \phi / \partial n = 0$ , 介质边界上; (4)

V 是计算电容时在导体上加的电压,一般取为 1 , n 指边界上的单位法向量。另外,该结构的上、下表面接地。在介质层中,利用分离变量法,令  $\phi(x,y,z)=T(x,y)L(z)$  ,代入 (1) 式可得

$$\partial^2 T/\partial x^2 + \partial^2 T/\partial y^2 + \alpha^2 T = 0, \qquad \partial^2 L/\partial z^2 - \alpha^2 L = 0.$$

(5)

代入(3)式可知, T(x,y)在各介质层中满足的条件为

$$\partial T/\partial x = 0, \quad x = 0, a; \quad \partial T/\partial y = 0, \quad y = 0, b;$$

(6)

而在含有导体的各层中,为利用分离变量法必须先将边界条件齐次化,令

$$\phi(x,y,z) = 1 + \psi(x,y,z),\tag{7}$$

其中  $\psi(x,y,z)$  满足 Laplace 方程和下面的齐次边界条件:

$$\psi(x, y, z) = 0$$

, 导体边界上;  $\partial \psi / \partial n = 0$ , 介质边界上, (8)

故可以分离变量如下:

$$\psi(x, y, z) = T(x, y)L(z). \tag{9}$$

代入 (1) 式可得到与 (5) 式相似的方程。但这里 T(x,y) 所满足的横向边界条件为

$$T(x,y) = 0$$

, 导体边界上;  $\partial T/\partial n = 0$ , 介质边界上; (10)

(5) 式中的前式与边界条件 (6) 式和边界条件 (10) 式可分别构成二维 Helmholtz 边值问题,这样相对于 (1) 式和边界条件 (3),(4) 式所构成的三维 Laplace 边值问题方程减少了一维。在任一介质层中二维 Helmholtz 方程有解析解,模式函数为

$$T_{pq}(x,y) = \sqrt{\frac{\varepsilon_p \varepsilon_q}{ab}} \cdot \cos \frac{(p-1)\pi x}{a} \cdot \cos \frac{(q-1)\pi y}{b}, \qquad p,q = 1,2,3,\dots$$

(11)

其中

$$\varepsilon_p = \begin{cases} 1, & p = 1; \\ 2, & p \ge 2; \end{cases} \qquad \varepsilon_q = \begin{cases} 1, & p = 1; \\ 2, & p \ge 2; \end{cases} \tag{12}$$

本征值为

$$\alpha_{pq} = \pi \sqrt{(\frac{p-1}{a})^2 + (\frac{q-1}{b})^2}, \qquad p, q = 1, 2, 3, \cdots.$$

(13)

而对于含有导体的各层的模式函数则需用数值办法求取、详述如下:

用二维不等步长有限差分网格对 (5) 式中的前式进行离散,并将所得到的 FD 方程写成矩阵方程的形式:

$$A\overline{T} = \alpha^2 \overline{T}. (14)$$

这是一个形如  $A\overline{T}=\lambda\overline{X}$  的本征值问题, A 矩阵的特征值对应于  $\alpha^2$  ,而其各特征向量  $\overline{T}_j$  的各元素值则为各模式函数在各离散点上的函数值。在得到各层的解析或数值模式函数和特征值以后,根据 (5) 式中的后式的通解,可得各层电位函数的形式解。在介质层中的解的形式为

$$\phi(x, y, z) = \sum_{p=1} \sum_{q=1} T_{pq}(x, y) [A_{pq} h_{pq}(z) + B_{pq} e_{pq}(z)], \tag{15}$$

其中

$$h_{pq}(z) = \begin{cases} \operatorname{ch}(\alpha_{pq}z), & p+q>2; \\ 1, & p=q=1; \end{cases} \qquad e_{pq}(z) = \begin{cases} \operatorname{sh}(\alpha_{pq}z), & p+q>2; \\ z, & p=q=1. \end{cases}$$

在含导体的各层中的解则为

$$\phi(x, y, z) = 1 + \sum_{j=1} [A_j \operatorname{ch}(\alpha_j z) + B_j \operatorname{sh}(\alpha_j z)] \varphi_j(x, y), \tag{16}$$

$\varphi_j(x,y)$  是第 j 个数值模式函数。在实际计算时,(15)、(16) 式中的模式展开系数的数目应截取成有限值。

下面的做法类似于模式匹配法。将各区的电位函数表达式 (15) 式或 (16) 式代入到各层介质交界面上的连续性条件 (2) 式中去,并用相应的模式函数在等式两边作内积,就可得关于各层的模式展开系数的方程,联立这些方程即可求得各层中的各模式展开系数,进而确定所有层中的电位函数。利用电位函数即可获得各导体表面的面电荷密度  $\rho_s$  ,则该互连结构的电容可以由面电荷密度方便地求出。

### 3 数值结果

我们用维数缩减技术编制了一个通用程序,可以快速、准确地提取出埋在任意层数的介质中,具有任意结构参数的通孔结构的准静态电容参数。下面举出一个例子,并给出与 Ansoft 软件的比较。

结构中介质层数为 7, 自下往上数,下信号线在第 2 层,上信号线在第 6 层,通孔穿过 3 层介质。由下而上,各层的介电常数依次为 3.9 、 2.45 、 2.45 、 3.9 、 3.9 、 2.45 、 1.0,厚度依次为 2.0mm 、 1.0mm , 1.0mm ,

| 液上 个问候式数组合下的订算值、订算的间、所用内仔和相对于 Anso |       |       |       |            | 相对于 Anson | 引读是      |      |

|------------------------------------|-------|-------|-------|------------|-----------|----------|------|

|                                    | MODE1 | MODE2 | MODE3 | CPU 时间 (s) | 内存 (Mb)   | 电容值 (pF) | 相对误差 |

|                                    | 49    | 35    | 35    | 49         | 0.707     | 1.023    | 3.1% |

|                                    | 49    | 40    | 40    | 51         | 0.711     | 1.031    | 2.3% |

|                                    | 49    | 45    | 45    | 53         | 0.713     | 1.032    | 2.3% |

表 1 不同模式数组合下的计算值、计算时间、所用内存和相对于 Ansoft 的误差

#### 4 结 论

本文应用维数缩减技术快速、准确地提取了埋在任意介质层中且上下信号线有厚度的通孔结构的准静态电容参数,而只用了很少的计算资源。由于该技术着眼于集成电路结构分层性的特点来发展高效算法,因而可以推广应用于各种多层介质中多导体互连结构的电容参数提取。

#### 参考文献

- [1] Wang T, Mautz J R, Harrington R F. The excess capacitance of a microstrip via in a dielectric substrate, IEEE Trans on CAD, 1990, CAD-9(1): 48-56.

- [2] Wang T, Harrington R, FMautz J R. Quasistatic analysis of a microstrip through a hole in ground plane, IEEE Trans. on MTT, 1988, MTT-36(6): 1008-1013.

- [3] KOP P, De Zutter D. Capacitance of a circular symmetric model of a via hole including finite ground plane thickness. IEEE Trans. on MTT, 1991, MTT-39(7): 1229-1234.

- [4] Mathis A W, Butler C M. Capacitance of circular symmetric via for microstrip transmission line, IEEE Proc. -H, 1994, 141(8): 265-271.

- [5] Faton Tefiku, Eidichi Yamashita. Efficient method for the capacitance calculation of circularly symmetric via in mutilayered media, IEEE Microwave and Guided Wave Letters, 1995, 5(9): 305-307.

- [6] Zhenhai Zhu, Wei Hong, et al. Electromagnetic modeling and transient simulation of interconnects in high speed VLSI, IEEE Multi-chip module conference MCMC' 95, Santa Cruz, California: 1995.

- [7] 朱震海,洪 伟,陈忆元. 集成电路中多导体传输线的电磁参数提取和瞬态响应分析. 电子学报, 1996, 24(6): 51-54.

- [8] C Wei, Harrington R F, et al. Multiconductor transmission lines in multilayered dielectric media, IEEE Trans. on MTT, 1984, MTT-32(4): 439-450.

# CAPACITANCE EXTRACTION OF THE VIA HOLE STRUCTURE EMBEDDED IN THE MULTILAYERED DIELECTRIC MEDIA

Song Ben Hong Wei

(Southeast University, Nanjing 210096)

Abstract An efficient method to calculate the quasi-static capacitance of the via hole structure embedded in a multilayered dielectric media named Dimension Reduction Technique(DRT) is presented. Since the method takes full advantage of the characteristics of the stratified structure in integrated circuit, it can easily deal with the varied numbers of the dielectric layers as well as the varied structure parameters while only need little CPU time and memory space. The numerical results given in this paper are in good agreement with those of Ansoft's software.

**Key words** Parameter extraction, Quasi-static capacitance, 3D interconnect, Via hole, Dimension Reduction Technique(DRT)

- 宋 犇: 男, 1973 年生, 硕士生, 目前研究方向为超大规模集成电路中多导体互连电磁参数的提取.

- 洪 伟: 男, 1962 年生, 教授, 博士生导师, 主要从事电磁理论与微波技术方面的科研与教学工作.